近日,西安电子科技大学微电子学院在高速模数转换芯片(ADC)方向取得重要进展。在集成电路设计领域国际顶级期刊JSSC ( IEEE Journal of Solid-State Circuits )上发表了题为“A 0.004-mm2 3.65-mW 7-bit 2-GS/s Single-Channel GRO-Based Time-Domain ADC Incorporating Dead-Zone Elimination and On-Chip Folding-Offset Calibration in 28-nm CMOS”的最新研究成果,西安电子科技大学为第一完成单位,微电子学院的张乘浩和尉江渤博士作为论文第一第二作者,刘马良教授、杨银堂教授和陈勇教授作为共同通信作者,该研究采用新型时间域转换架构实现了国际顶尖的高鲁棒性、高单通道转换速率、高能效ADC芯片。

据悉,高速高性能模数转换器是现代移动通信、宽带雷达、卫星定位、无线通信等电子系统的关键部件,也是欧美针对中国瓦森纳协议中管控的核心卡脖子器件。与此同时,纳米级工艺尺寸微缩导致芯片供电电压下降,器件本征增益降低,电容微缩受到限制,传统架构ADC芯片能效提高和面积微缩愈发困难。

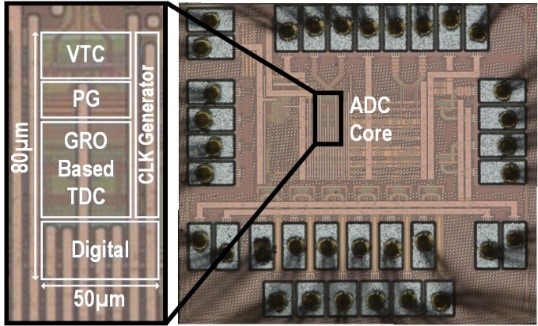

2GS/s 7位ADC芯片

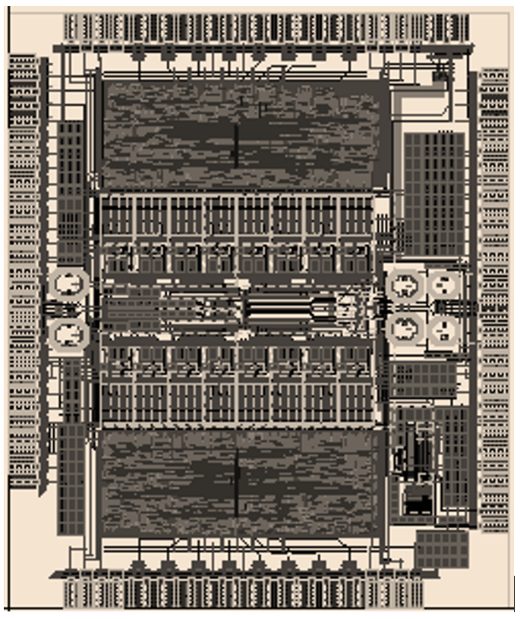

64GS/s 8位ADC芯片版图

据介绍,该研究提出一种基于门控环形振荡器的新型时间域模数转换架构,突破了高线性度时域信号处理电路设计,相比于传统架构有效提升了单通道转换速率,大幅降低了芯片功耗,并搭配精准的时序控制和高效数字辅助校准技术,实现了业内顶尖的高鲁棒性时间域模数转换芯片,核心面积仅为0.004-mm2。

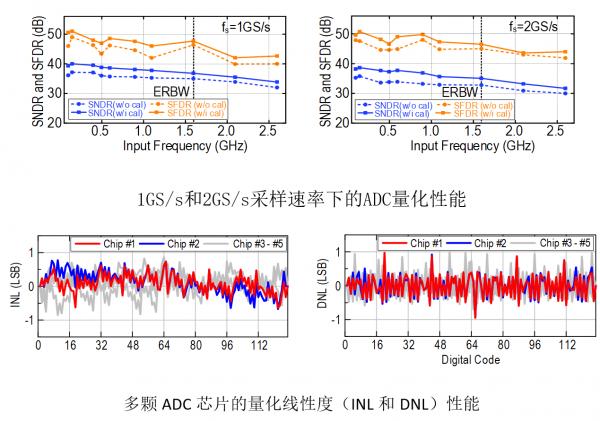

该ADC芯片在2GS/s的单通道采样速率下,可实现高于50dB的SFDR和大于1GHz的有效带宽,功耗仅为3.65mW,能效比在国际同指标ADC芯片中达到最优。多批次芯片其在工业温度范围和供电电压变化下SNDR性能波动小于1dB,具有良好的鲁棒性,且各项性能指标已通过工信部五所权威认证,是业内首批可实现量产的时间域ADC芯片。该架构ADC适应于未来的5nm、3nm等更先进制程工艺,并具备更好性能和更小面积的潜力,也是全数字化ADC发展的里程碑。